ディジタル回路のクロックは重要ですが、ちょうどいい水晶発振子がなかったりするときなど、クロック N 逓倍器があると便利な場合があります。

最近は 21.48MHz (3.58MHz x6) の水晶がなく、某所で中国製の水晶発振子を購入したらぜんぜん違う周波数で(基本波から違う)困ったことがあります。

PLL を組めば N 逓倍できますが、いまさら VCO + MC4044 という組み合わせの回路は設計が面倒です。

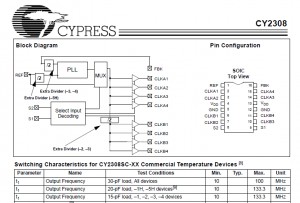

CY2308

最近 Cypress の CY2308 (+IDT23S08) という石をたくさん手に入れました。

これはもともとクロック分配の用途に作られた IC ですが、PLL を内蔵しており、フィードバック端子が外部に出ているので、ディバイダを外付けすれば手軽なクロック逓倍回路に使えそうです。

ただし出力周波数は10-133MHz と規定がありますが、入力周波数の規定がありません。

私が使用する周波数帯はだいたい 1-30MHz なので、この用途で使えるかどうかは基準周波数と発振周波数の下限(PLL 特性で決まる)にかかってきます。

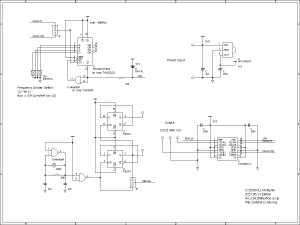

テスト回路

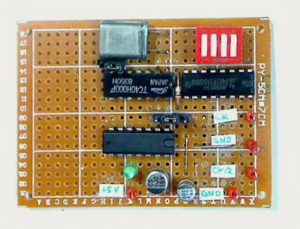

というわけでテスト回路を組んでみました。

使用したのは CY2308SC-2 なので CLK と CLK/2 が出力されます。

CY2308 の CLK/2 または CLK 出力を 74ALS161 の 1/N 分周器で分周して FBK 端子に戻しています。

FBK のデューティは 50% でなくてもいいようです。

基準周波数は TC40H000 で発振させた 3.58MHz で、その 1/2 と 1/4 も選択できるようにしています。

したがって、出力周波数は fout = (3.58 / M) x N (x 2) MHz となります。

この回路の最大周波数は分周器に依存しますが、CO – /LD 間に使った TC40H000 の伝達遅れが大きく、これをたとえば 74AS04 などにすれば CLKOUT = 80MHz 以上出せるはずです。

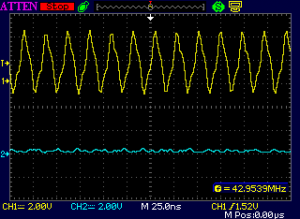

波形

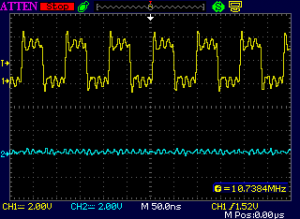

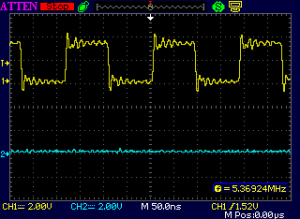

fREF = 3.58 MHz、N=3 の CLK 出力は上図で、CH1 が CLKOUT 信号の波形を示しています(以下同じ)。この程度の REF 入力なら問題ないようです。

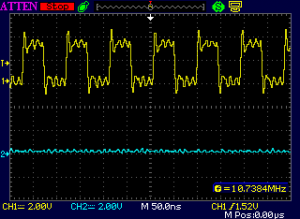

fREF = 1.79 MHz, N=6 の CLK 出力が上図で、fREF = 1.79 MHz はまだ大丈夫そうです。

fREF = 0.9MHz にすると CLK 出力が不安定になりました。(画像保存失敗)

よく使う 4MHz とか 6MHz のクロックなら、REF 入力にしても問題なさそうに見えます。

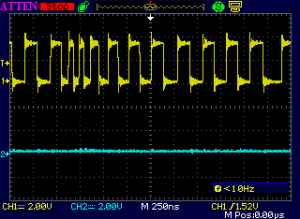

fREF = 1.79 MHz でどこまで出力周波数を下げられるかやってみます。

N=3 つまり fout = 5.37MHz はまだ安定しています。

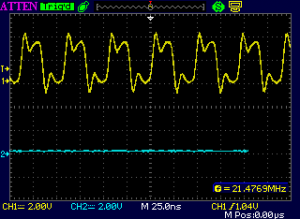

N=2 つまり fout=3.58MHz では出力周波数が不安定になりました。

5.37 MHz で OK とはいえ、温度変化を考えるとやはり出力周波数はできるだけ 10MHz 以上に設定するべきでしょう。

とりあえず最初にほしかった 21.48MHz が簡単に作れるようになったので満足です。