秋月電子のおたのしみ袋に CE-1025 と印字のあるモジュールが入っていました。データが見つからないので解析してみます。

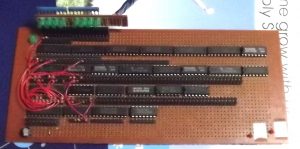

シールド内部はこのような基板が入っています。パワーインダクタがあることから、スイッチング電源モジュールのようです。

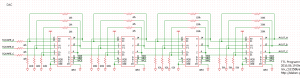

5 Pin や 6 Pin の石が見えますが、これは IC ではなく複合 Tr です。

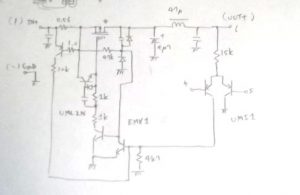

ROHM の UMS1、EMX1、UML2N が使用されているようです。

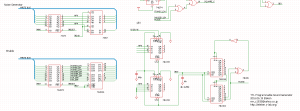

解析のためトレースした回路図が上図です。

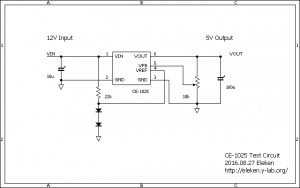

見ての通りステップダウンレギュレータの構成になっています。

回路構成から入力定格は 12-24V 程度だと思います。

図中右側の PNP Tr は誤差増幅で、

フィードバック電圧と基準電圧は外付けですから、

可変電圧 (Vout > 3.5V) の SW レギュレータとして使用できます。

上記解析より、CE-1025 は図のような回路により使用できます。