さて重要なのは DAC の設計です。

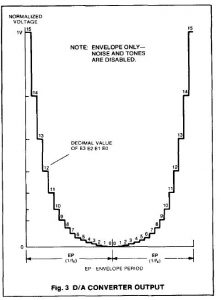

AY-3-8910 は各 ch 内部 4bit の表現を持ちますが、その出力 DAC は対数出力となっています。

対数出力ということは、ストレートに R-2R ラダーは使えません。

簡単に思いつく構成は以下の3 つ:

(1) 対数型 DAC を組む

(2) 74154 + 抵抗 16 個

(3) ディジタルで linear-log 変換をした後バイナリ DAC

独立 3ch 分の DAC を組まなければならないため、今回は一番構成部品の少ない (1) の構成で設計します。

ただし、(1) は「TTLで作る…」と銘打っておきながら CMOS IC を使うことになるので、TTL 縛りが重要なら (2) を採用することになります。オリジナルの IC は MOS によりますが・・・。

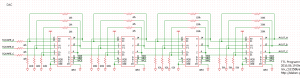

設計した DAC の回路図を示します。CMOS のアナログスイッチ 4053B は都合良く 3 回路入りなので、3ch の 4 bit DAC が わずか 4 個の IC で構成できます。

対数の底については、データシートの図表から LSB が -3dB (sqrt(1/2) 倍) になるように回路定数を設定しています。この定数が妥当かどうかはわかりません。出力インピーダンスは 47k となりますが、これは手持ちの抵抗値によって定数を適当に設定した結果です。