前回は AVR の VUSB で USB-PSG インタフェースを製作しましたが、速度的に問題がありました。

VUSB は USB Low Speed のみ対応していますが、規格上 LS のビットレートは最大 1.5Mbps なので、MIDI (31.25 kbps)程度の速度なら十分のように思っていました。

しかしながら、USB LS は バルク転送やアイソクロナス転送に対応しておらず、インタラプト転送で信号を送らなければいけません。

私の使用している Windows だとインタラプト転送のインターバルは最短 8ms、転送は最大 8 バイト(VUSB の仕様)なので、6バイト (2 MIDI メッセージ) / 8ms と考えると、実効ビットレートはわずか 6kbps しかありません。

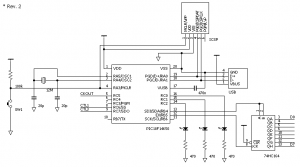

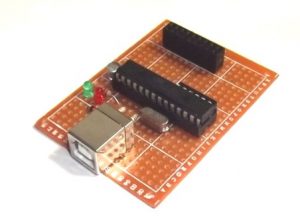

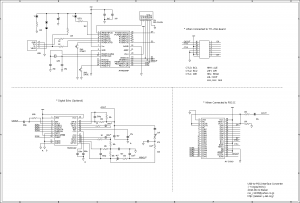

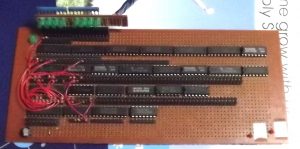

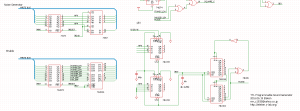

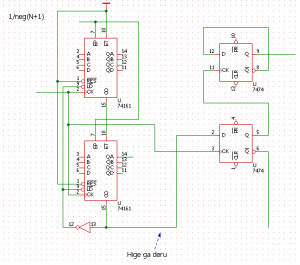

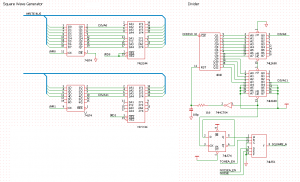

そういうわけで、USB2.0 に対応した PIC18F14K50 を使って、USB-PSG インタフェースを作り直しました。

(秋月ではいつの間にか 170 円から 210 円に値上がりしていますね…)

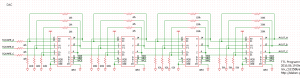

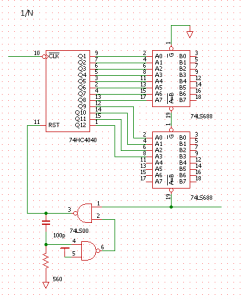

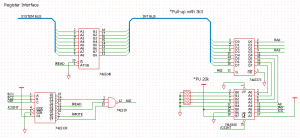

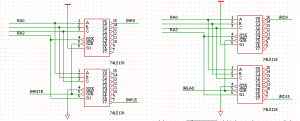

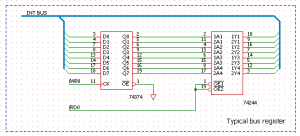

外観は前回とほとんど変わりませんが、ピン数の関係で SIPO SREG の 74HC164 を追加しています。

PIC の場合、Microchip Library for Applications (MLA) に含まれる USB サンプルをもとに USB デバイスを実装するのが便利です。

今回は「audio_midi」サンプルをベースに 仮想 USB デバイスを実装しています。

VID/PID とかデバイスディスクリプタは適宜書き換える必要があります。

今回はあくまで TTL-PSG のテスト用ということで、サンプルのままにしています。

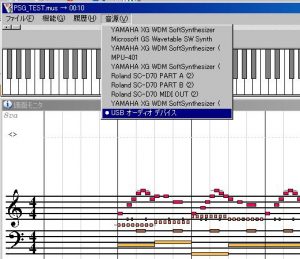

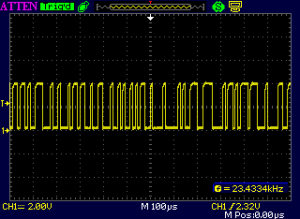

USB2.0 のバルク転送だけあって、転送は USB LS のものよりはるかに高速になります。

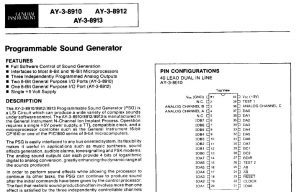

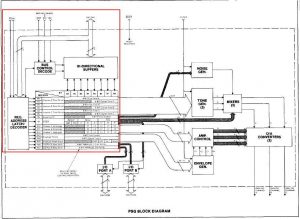

これで、PC から PSG 音源のまともな演奏ができるようになりました。