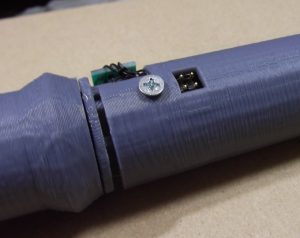

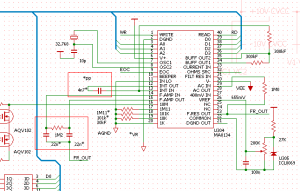

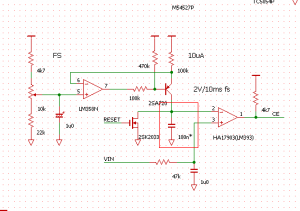

一般的に、アナログ回路などでコンデンサの特性が回路上重要になる場合、100pF – 100nF 程度の容量値ではセラミックコンデンサではなくフィルムコンデンサを使用します。回路図上ではコメントで表記したり、値に「*」記号を付加して区別したりします。たとえば私の書いた回路図では、下図のようになっています。

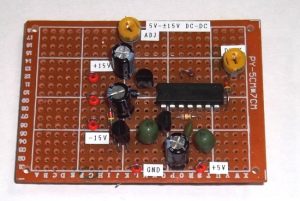

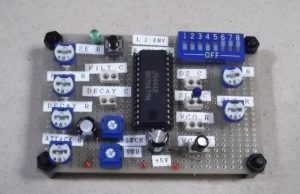

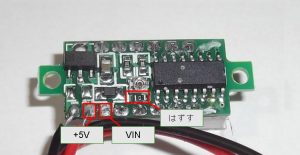

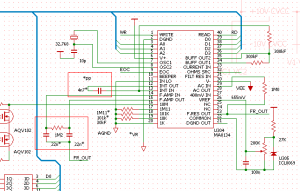

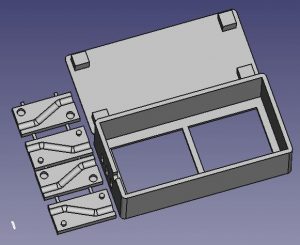

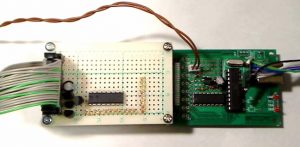

例1:半導体カーブトレーサ(未公開)

例1:半導体カーブトレーサ(未公開)

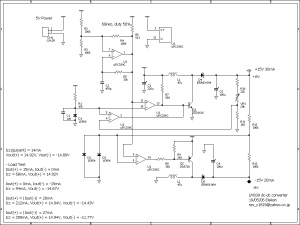

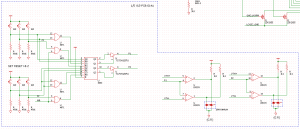

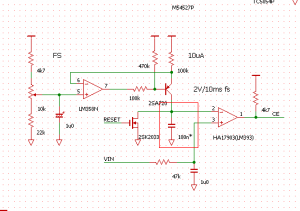

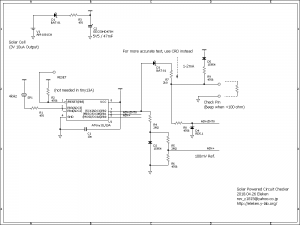

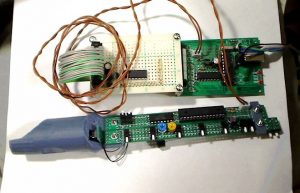

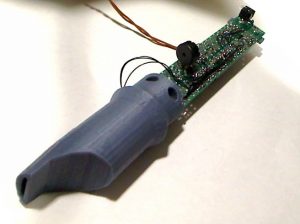

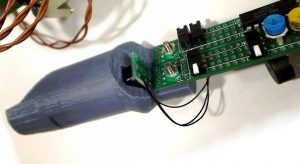

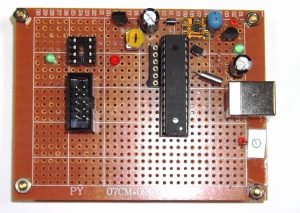

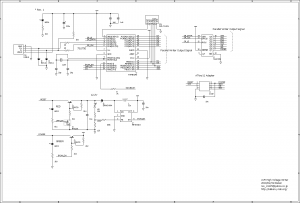

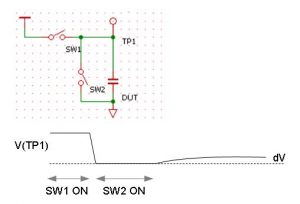

例2:ミリオーム計

例2:ミリオーム計

赤枠で囲ったコンデンサはその特性が重要になるのでフィルムコンデンサ指定です。とくに例1の積分コンデンサにはポリプロピレンコンデンサを指定しています。ミリオーム計ではこの点について質問をいただきましたので、説明が必要でしたね。

なおフィルムコンデンサを種類指定で購入する場合、そこらの小売店だと型番、種類が曖昧で販売していることがあるので、信頼できる店で購入することが望ましいです。たとえばポリプロピレンフィルムコンデンサ指定で探す場合などは RS コンポーネンツで購入するといいと思います。

で、フィルムコンデンサといってもいろいろありますので、当記事では各コンデンサの特徴と損失係数 D をみていきます。

損失係数 D とは

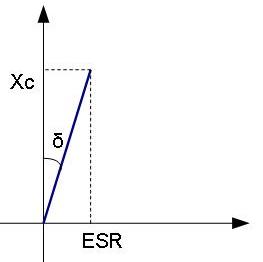

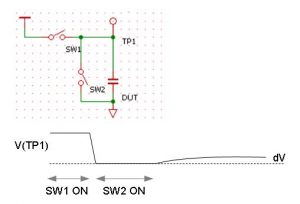

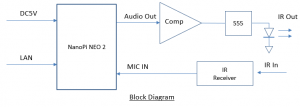

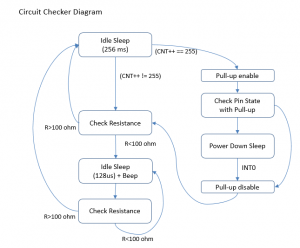

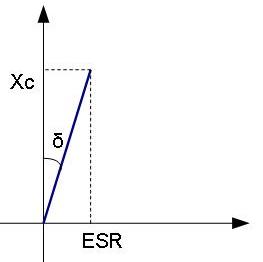

(適当なイメージ図)

(適当なイメージ図)

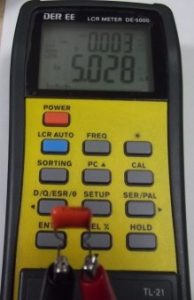

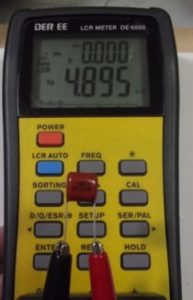

損失係数はひとことで言うと、コンデンサのコンデンサ成分とよけいな成分の割合です。理想的なコンデンサは損失 0 ですが、実際は ESR (等価直列抵抗) に代表されるような損失があります。これは、コンデンサに AC 電圧を付加したときの電流の位相(理想は90°)としてみることができます。上図のように、両成分の割合=90°からの位相差 δ の正接 (tanδ) をとったものが D です。したがって理想的なコンデンサであれば D=tanδ=0 となり、これが高いほど波形ひずみや。フィルムコンデンサのカタログでは D の % 表示、電解コンデンサのカタログでは tanδ で表記することが多いです。なお D は LC メータで計測できます。

誘電体吸収とは

コンデンサに電荷の溜まった状態で両端子を短絡させると、当然端子間の電位差は 0V となります。ところがこの状態から端子間を開放して少し経つと両端子間に電位差が現れます。このような現象を誘電体吸収といいます。誘電体吸収は損失係数とは無関係で、誘電体の材質により現象の起こりやすさが変わります。

実際に誘電体吸収を観測しようとすると少し大変(シールドをしっかりして、J-FET 入力 OPAMP を使えば可能だと思います)なので、別の機会にゆずります。

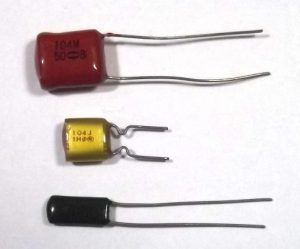

いろんなフィルムコンデンサ

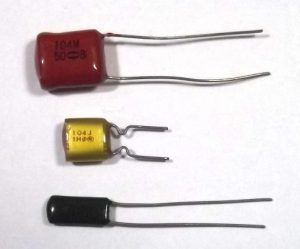

手元にあったコンデンサをみていきます。どうもパ行が多くややこしいので、文中では PET コンデンサ、PP コンデンサ、PS コンデンサなどと略すことにします。

PET: ポリエチレンフィルムコンデンサ(ポリエステルフィルムコンデンサ)

金属箔とPET (ポリエチレンテレフタレート) フィルムを巻いたもので、フィルムコンデンサの中でも一番安価で、一般的に使われます。おおむね耐圧 50-200V 程度で、100pF – 1uF 程度の容量値の製品が手に入ります。マイラコンデンサと呼ばれることがありますが同じものです。温度係数>0。

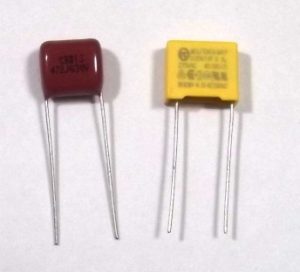

メーカによって黄色や白の透明外装だったり、茶色かったり、ガムのような形状だったりしますが、最近のものであれば性能はどれも変わりありません。

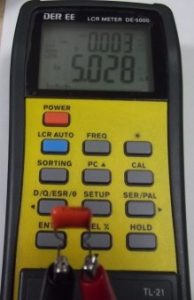

写真のように、いずれも D = 0.003 程度を示します。セラミックコンデンサ (D=0.008 – 0.05) や電解コンデンサと比較するととても低い値であり、大抵のアナログ回路にはこれで十分です。フィルムを巻いている関係で高周波回路に向かない点と、誘電体吸収が若干ある点に注意が必要です。良い特性を要求される積分コンデンサにはあまり向きません。(INL 0.1% 程度悪化します)

M-PET: メタライズドポリエチレンフィルムコンデンサ

ポリエチレンコンデンサの高耐圧版で、1kV 程度までの製品があります。また、自己回復作用(いったん短絡しても、電源を入れなおすと回復する)を持ちます。それ以外の性能はポリエチレンコンデンサとほとんど同じです。上記コンデンサを積層型にしたものもあり、同容量・同耐圧ならば小型になります。いろんな形状があります。

D=0.3% – 0.5% と、実測上、通常の PET コンデンサよりも高い損失係数を示す傾向にあります。一番右側は DF コンデンサで、-55/+125℃範囲品です。

PP: ポリプロピレンフィルムコンデンサ

PET のかわりに PP (ポリプロピレン) を使用したもので、高耐圧コンデンサとしてポピュラですが、それ以上にコンデンサとしての性能が優れています。そのかわりにやや高価です。おおむね、ポリエチレンコンデンサと同様の容量範囲の製品が入手可能です。温度係数<0。

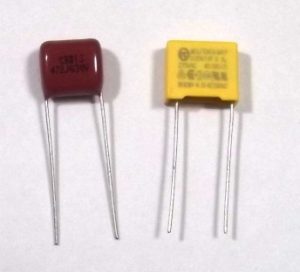

左側の製品のように、見た目からは PET コンデンサと区別することは難しいです。

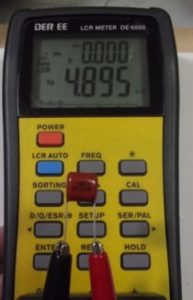

写真のように D=0.000 と非常に低い値を示すので、ここで PET との違いを判断できます。PP コンデンサは誘電体吸収もほとんど示しません。これらの特性から計測器の(とくに 積分型 ADC の)積分コンデンサに最適です。D=0 ということから AC を流してもほとんど発熱しませんので、高電圧 AC のカップリング、分圧コンデンサとしても適しています。

一番左のは巨大なコンデンサですが、強電になると損失による発熱が無視できないわけで、損失の少ない PP コンデンサが使われます。

PS: ポリスチレンフィルムコンデンサ

日本ではスチロールコンデンサ、スチコンと呼ばれることがほとんどですが、要するにポリスチレンを巻いたコンデンサです。コンデンサとしての性能は優れていますが、耐圧がポリプロピレンコンデンサほど高くないことと、誘電体吸収は PET コンデンサよりも少し大きいようです。高い容量の製品はなく、100p – 10nF くらいが一般的な容量レンジです。また、熱に弱いため半田付けの際は注意が必要です。またこの性質のため SMD 化は不可能であり、古くからあるコンデンサですが、いまや絶滅危惧種です。温度係数<0。

D=0.000 と測定限界以下です。すばらしい。右側のは NEC の50年前のコンデンサです。

PET-PP: ポリエチレン・ポリプロピレンコンデンサ

フィルムコンデンサを使用して時定数回路を作ると温度による変化が問題となります。ポリエチレンコンデンサは温度係数>0、ポリプロピレンコンデンサは温度係数<0 です。そこで、ポリエチレン、ポリプロピレンの両方を使用して、温度係数を常温で 0 に近づけたものがこのコンデンサです。これを使えば、抵抗側で温度係数の補償をすることなく、広い温度範囲で比較的安定な発振器やタイマ回路を作ることができます。しかしながら、今は PEN (ポリエチレンナフタレート) コンデンサに置き換わってしまい、絶滅危惧種です。

上写真は日精 AWS シリーズ(現行品ではない?)ですが、D =0.2% なのでちょうどポリエチレン、ポリプロピレンの中間になっています。

まとめると

- 損失係数でみると、ポリプロピレン (PP) コンデンサ>ポリスチレン (PS) コンデンサ>ポリエチレン (PET) コンデンサ>メタライズドポリエチレンコンデンサの順で良好。

- 積分コンデンサなど性能が重要なコンデンサには、PP コンデンサを使用すべし。

- PP コンデンサと PET コンデンサは損失係数の測定で判別可能。

- 見た目で区別できないので、測定機器がない場合には信頼できる店で購入。

- PET コンデンサの見た目で性能に違いはなさそう。